intersil

# EL7761

# NO RECOMMENDED REPLACEMENT NU KEUUNINIENUEU KEFLAUENIENI contact our Technical Support Center at contact our recnnical support venter at 1-888-INTERSIL or www.intersil.com/tsc January 1996, Rev C

#### FN7299

## 100V Half Bridge Driver

The EL7761 provides a low cost solution to many half bridge applications. The EL7761 is DC

OBSOLETE PRODUCT

coupled so that there are no start up problems associated with AC coupled schemes. A single resistor from D<sub>SFT</sub> to GND provides "dead time" programmability. Shorting DSET to V<sub>DD</sub> gives the shortest delay (~100ns).

The POL pin controls the polarity of the low side driver. The polarity of the upper driver is always inverting. The EN pin, when low, forces the high and low side outputs into their low state.

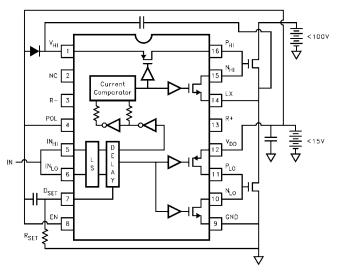

#### Pinout

#### EL7761 (16-PIN PDIP, SOIC) TOP VIEW

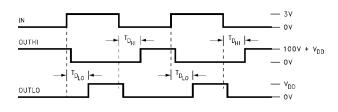

#### **EL7761 WAVEFORM EXAMPLE**

#### Features

- 100V High Side Voltage

- Programmable Delay

- **Direct Coupled**

- No Start Up Ambiguity

- · Rail to Rail Output

- 1MHz Operation

- Shutdown Function

- 1.0 Amp Peak Current

- Improved Response Times

- Matched Rise and Fall Times

- Low Supply Current •

- Low Output Impedance

- Low Input Capacitance

#### Applications

- Uninterruptible Power Supplies

- **Distributed Power Systems**

- **IGBT** Drive

- **DC-DC Converters**

- Motor Control

- Power MOSFET Drive

- Switch Mode Power Supplies

#### Ordering Information

| PART<br>NUMBER | TEMP. RANGE    | PACKAGE     | PKG. NO.      |

|----------------|----------------|-------------|---------------|

| EL7761CN       | -40°C to +85°C | 16-Pin PDIP | MDP0031       |

| EL7761CS       | -40°C to +85°C | 16-Pin SOIC | MDP0027(Note) |

NOTE: Contact factory

|          | POL                    | POLARITY                   |

|----------|------------------------|----------------------------|

| Low Side | GND<br>V <sub>DD</sub> | Inverting<br>Non-Inverting |

| Hi Side  | Х                      | Inverting                  |

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

| Supply (V <sub>HI</sub> to GND) | Storage Temperature Range65°C to +150°C    |

|---------------------------------|--------------------------------------------|

| Supply (V <sub>DD</sub> to GND) | Ambient Operating Temperature40°C to +85°C |

| Input Pins                      | Operating Junction Temperature             |

| +0.3V above V <sub>DD</sub>     | Power Dissipation                          |

| Peak Current per Output         | SOIC                                       |

|                                 | PDIP                                       |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

| PARAMETER           | DESCRIPTION                           | TEST CONDITIONS                | MIN   | ТҮР | MAX   | UNITS |

|---------------------|---------------------------------------|--------------------------------|-------|-----|-------|-------|

| INPUT/OUTPUT        |                                       |                                |       |     |       |       |

| V <sub>IH</sub>     | Logic "1" Input Voltage               |                                | 3.0   | 2.4 |       | V     |

| I <sub>IH</sub>     | Logic "1" Input Current               |                                |       | 0.1 | 10.0  | μA    |

| V <sub>IL</sub>     | Logic "0" Input Voltage               |                                |       | 1.8 | 0.8   | V     |

| IIL                 | Logic "0" Input Current               |                                |       | 0.1 | 10.0  | μA    |

| V <sub>HVS</sub>    | Input Hysteresis                      |                                |       | 0.5 |       | V     |

| V <sub>ENH</sub>    | Enable Threshold                      | Positive Edge                  | 2.8   | 1.6 |       | V     |

| V <sub>ENL</sub>    | Disable Threshold                     | Negative Edge                  |       | 0.9 | 0.6   | V     |

| V <sub>EN HYS</sub> | Enable Hysteresis                     |                                |       | 0.7 |       | V     |

| IDS OFF             | Output Leakage                        | $GND \leq V_{OUT} \leq V_{DD}$ | -10.0 | 0.2 | 10.0  | μA    |

| R <sub>OH</sub>     | Pull-up Resistance                    | I <sub>OUT</sub> = -100mA      |       | 5.0 | 10.0  | Ω     |

| R <sub>OL</sub>     | Pull-down Resistance                  | I <sub>OUT</sub> = +100mA      |       | 5.0 | 10.0  | Ω     |

| I <sub>PK</sub>     | Peak Output Current                   |                                |       | 1.0 |       | А     |

| I <sub>DC</sub>     | Continuous Output Current Source/Sink |                                | 50.0  |     |       | mA    |

| POWER SUPPL         | Ŷ                                     |                                |       |     |       |       |

| I <sub>DD</sub>     | Supply Current into V <sub>DD</sub>   | R <sub>SET</sub> = 5.1k        |       | 6.0 | 10.0  | mA    |

| I <sub>HI</sub>     | Supply Current into V <sub>HI</sub>   |                                |       | 2.0 | 4.0   | mA    |

| IDD OFF             | Supply Current into V <sub>DD</sub>   | V <sub>EN</sub> = 0.6V         |       |     | 750.0 | uA    |

| V <sub>DD</sub>     | Operating Voltage                     |                                | 4.5   |     | 15.0  | V     |

**DC Electrical Specifications**  $T_A = 25^{\circ}C$ ,  $V_{DD} = 15V$ ,  $C_{LOAD} = 1000$  pF, unless otherwise specified

## AC Electrical Specifications $T_A = 25^{\circ}C$ , $V_{DD} = 15V$ , $C_{LOAD} = 1000$ pF, unless otherwise specified

| PARAMETER               | DESCRIPTION                            | TEST CONDITIONS                                                          | MIN                   | TYP                      | MAX                      | UNITS |

|-------------------------|----------------------------------------|--------------------------------------------------------------------------|-----------------------|--------------------------|--------------------------|-------|

| SWITCHING CHA           | RACTERISTICS                           |                                                                          |                       |                          |                          |       |

| t <sub>R</sub>          | Rise Time                              | C <sub>L</sub> = 500pF<br>C <sub>L</sub> = 1000pF                        |                       | 15.0<br>20.0             | 40.0                     | ns    |

| t <sub>F</sub>          | Fall Time                              | C <sub>L</sub> = 500pF<br>C <sub>L</sub> = 1000pF                        |                       | 15.0<br>20.0             | 40.0                     | ns    |

| <sup>t</sup> D ON HI    | High Side Turn On Delay Time           | $D_{SET} = V_{DD}$ $R_{SET} = 5.1k$ $R_{SET} = 400k$                     | 50.0<br>75.0<br>750.0 | 100.0<br>125.0<br>1150.0 | 150.0<br>200.0<br>1500.0 | ns    |

| <sup>t</sup> D ON LO    | Low Side Turn On Delay Time            | $D_{SET} = V_{DD}$<br>R <sub>SET</sub> = 5.1k<br>R <sub>SET</sub> = 400k | 50.0<br>75.0<br>750.0 | 100.0<br>125.0<br>1150.0 | 150.0<br>200.0<br>1500.0 | ns    |

| <sup>t</sup> D OFF HI   | High Side Turn Off Delay Time          | D <sub>SET</sub> = V <sub>DD</sub>                                       |                       | 100.0                    | 150.0                    | ns    |

| <sup>t</sup> D OFF LO   | Low Side Turn Off Delay Time           | D <sub>SET</sub> = V <sub>DD</sub>                                       |                       | 100.0                    | 150.0                    | ns    |

| <sup>t</sup> D MISMATCH | High to Lo Side Turn On Delay Mismatch | R <sub>SET</sub> = 400k                                                  |                       |                          | ±10.0                    | %     |

## Pin Descriptions

| PIN # | NAME             | FUNCTION                                                                                         |

|-------|------------------|--------------------------------------------------------------------------------------------------|

| 1     | V <sub>HI</sub>  | Positive supply for the high side driver.                                                        |

| 2     | NC               |                                                                                                  |

| 3     | R <sup>-</sup>   | Internal connection between the low side and high side driver. This pin is normally unconnected. |

| 4     | P <sub>OL</sub>  | Controls the polarity of the low side driver.                                                    |

| 5     | IN <sub>HI</sub> | Logic input for the high side driver.                                                            |

| 6     | IN <sub>LO</sub> | Logic input for the low side driver.                                                             |

| 7     | D <sub>SET</sub> | Connection for the delay adjust resistor.                                                        |

| 8     | EN               | A high voltage on this pin enables the part.                                                     |

| 9     | GND              | Negative supply of the low side driver and control circuitry.                                    |

| 10    | N <sub>LO</sub>  | Low side driver output pull down.                                                                |

| 11    | P <sub>LO</sub>  | Low side driver output pull up.                                                                  |

| 12    | V <sub>DD</sub>  | Positive supply of the low side driver and control circuitry.                                    |

| 13    | R <sup>+</sup>   | Internal connection between the low side and high side driver. This pin is normally unconnected. |

| 14    | LX               | Negative supply for the high side driver.                                                        |

| 15    | N <sub>HI</sub>  | High side driver output pull down.                                                               |

| 16    | P <sub>HI</sub>  | High side driver output pull up.                                                                 |

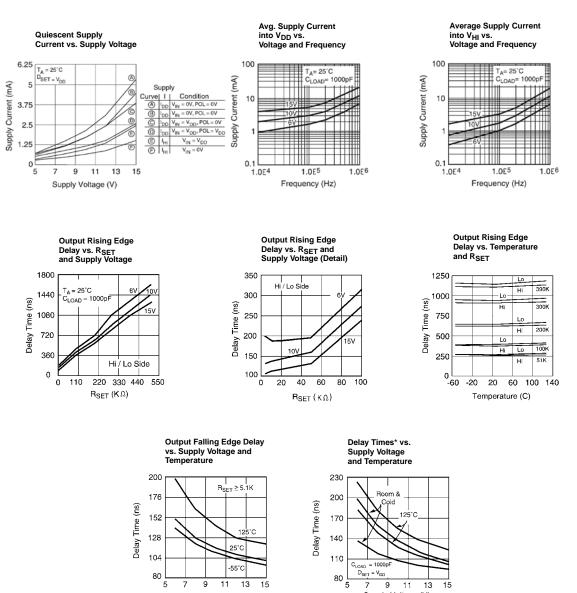

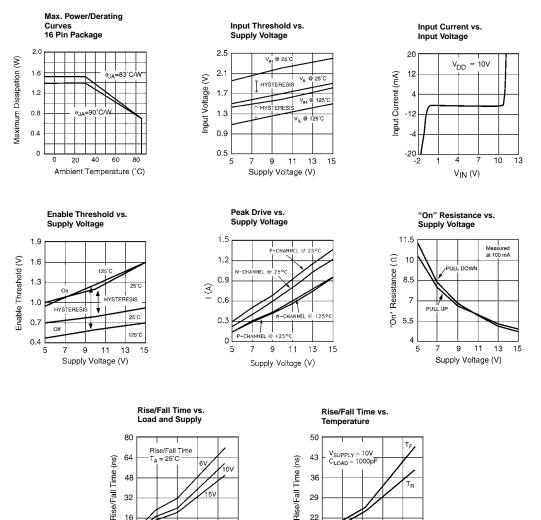

## **Typical Performance Curves**

\*Minimum Rising and Falling Edge Delay Time

Supply Voltage (V)

$V_{DD}\left(V\right)$

### Typical Performance Curves

22

15

-60 -20 20 60

100

Temperature (\*C)

140

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 guality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

16

0

0

500 1000 1500 2000 2500

Load Capacitance (pF)